# BACKNUMBERS

February 1980 Passion Meter, Win Indicator, Short Circuit Special, Kit Review Special, Into Electronics **Construction Part 1.**

#### May 1980

MiniClocks, 5080 Preamp, Model Railway Track Cleaner, 5080 Loudspeakers, Loudspeaker Crossover Design, Radio Controlled Model Survey.

#### June 1980

Microbe Radio Control System, Egg Timer, Two Watt Amplifier, Fog Horn, Short Circuits, LEDs and LED Displays.

July 1980 Sound-Operated Flash Trigger, 18 + 18 Car Stereo Booster, Hazard Flasher, Electronics in Photography, Electronic Espionage, Piezo Electricity.

#### August 1980

EquiTone Car Equaliser, Pass-The-Loop Game, Gaztec Gas Detector, OP-Amp Checker, In-Car Entertainment Survey, Introducing Microprocessors.

September 1980 MicroMixer, Reaction Tester, Guitar Phaser, Development Timer, Teletext Explained, Into **Digital Electronics Part 1.**

October 1980 Kitchen Timer, Tug 'o' War Game, Light Dimmer, Freezer Alarm, Intruder Alarm, Temperature-Controlled Soldering Iron.

January 1981 Car Rev-Counter, Bench Amplifier, Sound-Into-Light Converter, Chuffer, Electronic Games reviewed.

February 1981 Heartbeat Monitor, High-Impedance Voltmeter, Medium Wave Radio, Two-Tone Train Horn, Audio Signal Generator.

March 1981 Public Address Amplifier, Windscreen Wiper Controller, Bicycle Speedometer, Photographic Timer, Microcassettes.

#### April 1981

Pre-Amplifier Part 1, Super Siren, Guitar Tremolo, Russian Roulette Game, Doorbell Monitor, Anatomy of a Space Shuttle.

May 1981

Electronic Organ, Voice-Operated Switch, Infra-Red Controller, Pre-Amplifier Part 2, Audio Millivoltmeter.

June 1981 Power Amplifier Part 1, Continuity Checker, Envelope Generator, Early Radio, Gadgets, Games and Kits Supplement.

#### July 1981

Burglar Alarm, Doorbuzzer, Treble Booster, Electronic Aids for the Disabled, Power **Amplifier Part 2.**

#### August 1981

**Electronic Ignition**, Thermometer, Electronic Organ (final part), RPM Meter, Bench Power Supply, Radio Control Survey, Into Electronic **Components Part 1.**

All of the 1980 issues, except January and April, are still available together with the remaining issues from 1981

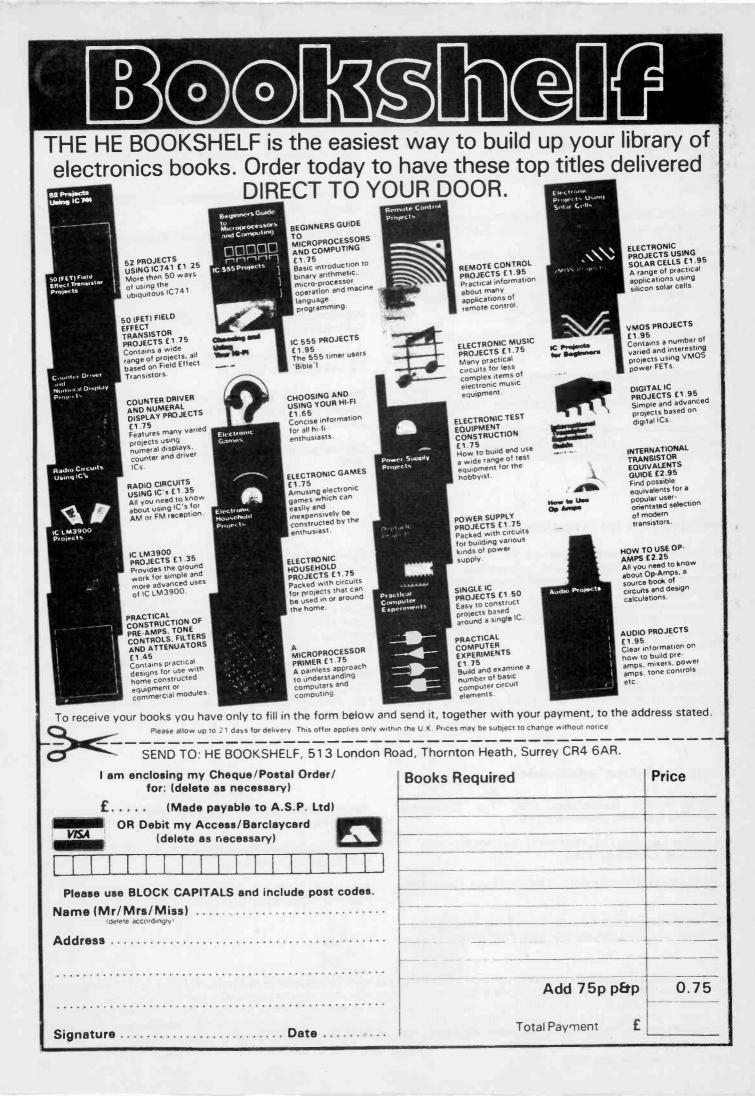

All backnumbers  $\cot t 1.50$  each. For those of you who only want copies of articles, we do offer a photocopying service. Each copy costs £1.50 and information as to its title and publication date should be given. Ordering backnumbers and photocopies could hardly be easier, just fill in the coupon, cut it out and send it to the appropriate address.

| HOBBY | ELECTR | ONICS |      |     |

|-------|--------|-------|------|-----|

| BACKN | UMBER  | ORDER | FORM | TO: |

513, London Road. Thornton Heath, Surrey, CR4 6AR England.

PHOTOCOPY ORDER FORM TO:

**HOBBY ELECTRONICS**

fold w FISICH TROUCION

145 Charing Cross Road, London, WC2H OEE

Please send me the following items:

| Please send me the following items: | Please send me the following items:                                         |

|-------------------------------------|-----------------------------------------------------------------------------|

| NAME                                | NAME                                                                        |

| ADDRESS                             | ADDRESS                                                                     |

| *****                               |                                                                             |

|                                     |                                                                             |

|                                     | Photocopies ofin the                                                        |

| Back issuesat £1.50 each            | issue at £1.50 each                                                         |

| l enclose £                         | I enclose f<br>Cheques and Postal Orders should be made paγable to ASP Ltd. |

# Volume 4 No. 2

# **GATEWAY TO ELECTRONICS**

EDITORIAL OFFICE: 145 CHARING CROSS RD LONDON WC2H 0EE

Edited and produced by Helen P. Armstrong

Technical Editor A. S. Armstrong

Idea by Dave Bradshaw

**Managing Editor Ron Harris**

Advertisement Manager David Kitchener

Assistant Advertisement Manager Joanne James

Managing Director T. J. Connell

PUBLISHED BY: Argus Specialist Publications Ltd., 145 Charing Cross Road, London WC2H 0EE. DISTRIBUTED BY: Argus Press Sales & Distribution Ltd., 12-18 Paul Street, London EC2A 4JS (British Isles). PRINTED BY: QB Limited, Colchester. ©Argus Specialist Publications Ltd 1983. All material is subject to worldwide copyright protection.

©Argus Specialist Publications Ltd 1983. All material is subject to worldwide copyright protection. All reasonable care is taken in the preparation of the magazine contents, but the publishers cannot be held legally responsible for errors. Where mistakes do occur, a correction will normally be published as soon as possible afterwards. All prices and data contained in advertisements are accepted by us in good faith as correct at time of going to press. Neither the advertisers nor the publishers can be held responsible, however, for any variations affecting price or availability which may occur after the publication has closed for press.

◄ Subscription rates upon application to ETI Subscriptions Department, 145 Charing Cross Road, London WC2H 0EE.

# CONTENTS

| -1 |                                                                        |                                                                         |

|----|------------------------------------------------------------------------|-------------------------------------------------------------------------|

|    | INTRODUCTION                                                           | CPU:                                                                    |

|    | What's it all about?4                                                  | Z840060                                                                 |

|    | MICROPROCESSORS                                                        | SUPPORT ICs:                                                            |

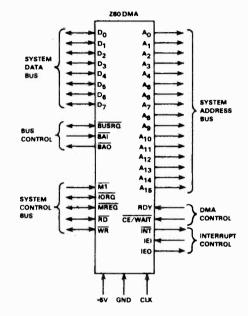

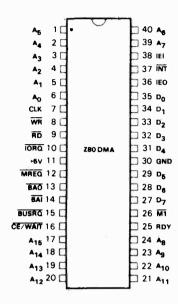

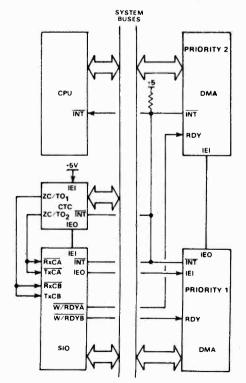

|    | The nature of the beast4                                               | 8420 PIO, 3801 STI, 3882 CTC,<br>3883 DMA, 3884 SIO, Z80                |

|    | THE 6800 FAMILY AND ITS                                                | DART64                                                                  |

|    | DERIVATIVES                                                            | CPU:                                                                    |

|    | CPUs:                                                                  | NSC 80076                                                               |

|    | 6800 Family6<br>68029                                                  |                                                                         |

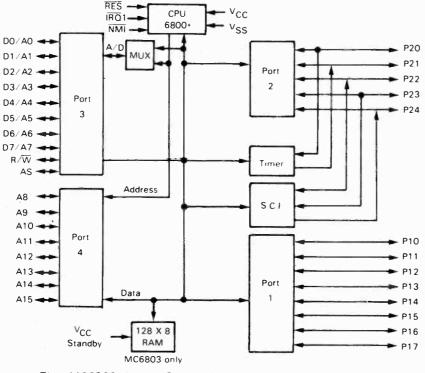

|    | 680312                                                                 | OTHER CPUs                                                              |

|    | 680916                                                                 | TMS 999578<br>INS 8073                                                  |

|    | SUPPORT ICs:                                                           | MK6800090                                                               |

|    | 6810, 6821, 6840, 6843,<br>6844, 6845, 6847, 6850,                     | MEMODIEC                                                                |

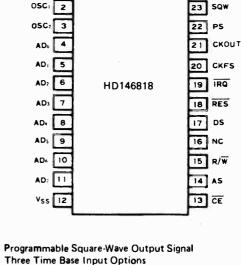

|    | 6852, HD146818,<br>F3846/F685622                                       | MEMORIES                                                                |

|    | F3846/F685622<br>CPU:                                                  | PROMS:                                                                  |

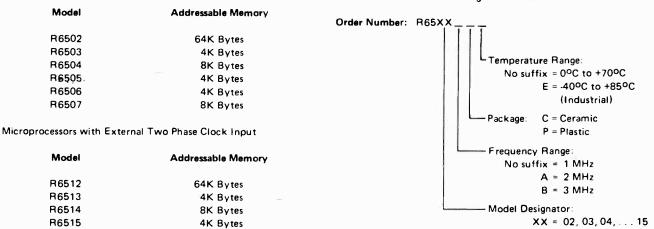

|    | 6500, 650231                                                           | 2716, 87C32, 276486                                                     |

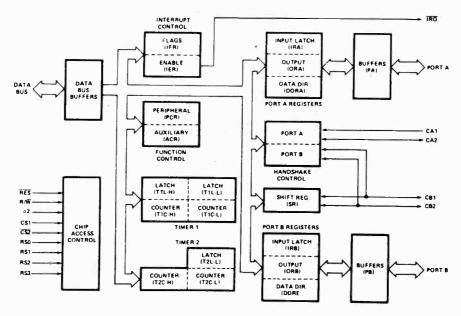

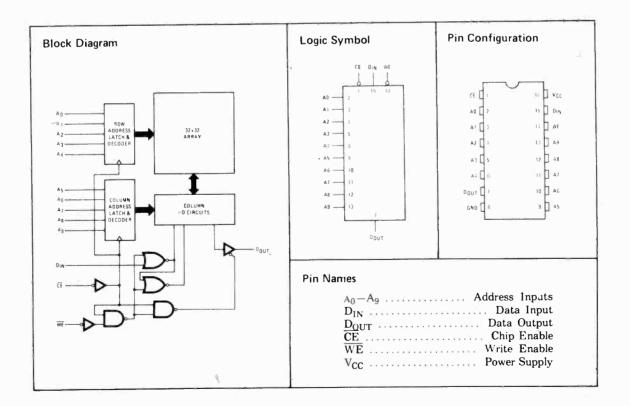

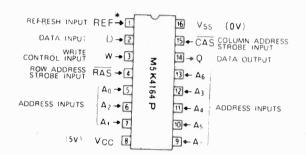

|    | SUPPORT ICs:<br>6522, 6520, 6532, 6545,                                | 4118, 6116, 5101,                                                       |

|    | 6592                                                                   | 6508, 4164, 402784                                                      |

|    | THE 8080 FAMILY AND ITS                                                | MISCELLANEOUS                                                           |

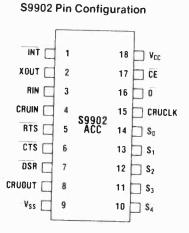

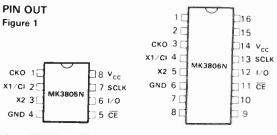

|    | DERIVATIVES                                                            | S9902, MK380581<br>SN74LS373                                            |

|    | CPUs:                                                                  | CHIP CHASING                                                            |

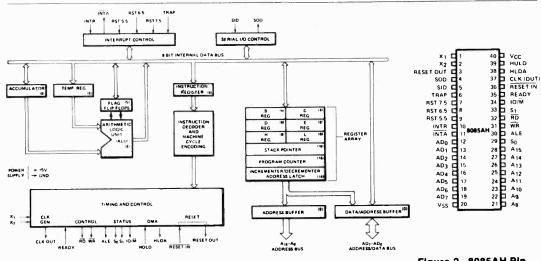

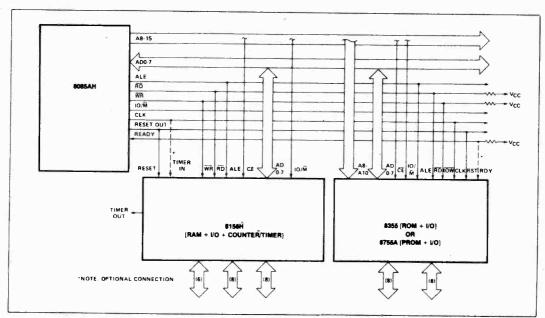

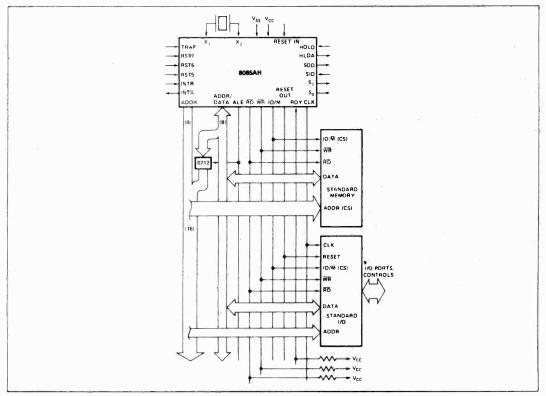

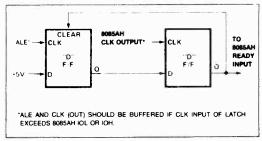

|    | 8085                                                                   | How and where to                                                        |

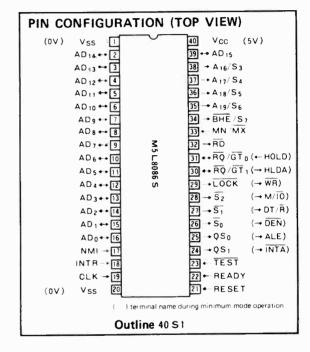

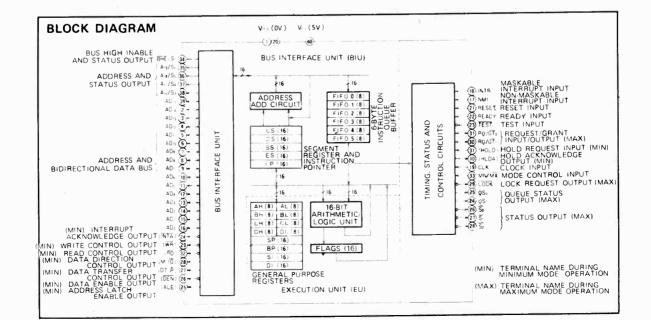

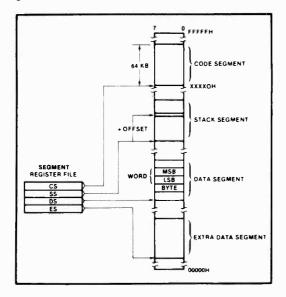

|    | 808645<br>808847                                                       | hunt them91<br>ADDRESSES                                                |

|    | SUPPORT ICs:                                                           | Manufacturers and                                                       |

|    | 8155, 8185, 8212,                                                      | Distributors                                                            |

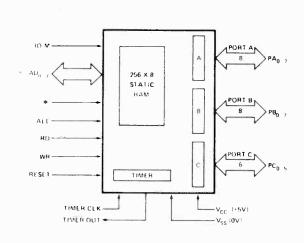

|    | 8254, 8255, 875552<br>Additional Systems                               | What to swot97                                                          |

|    |                                                                        | MPU GLOSSARY99                                                          |

| ,ł | acturers and by the editors to make the data contained in this edition | as accurate as possible, no liability in respect of its use is accepted |

Note: While every effort has been made by the manufacturers and by the editors to make the data contained in this edition as accurate as possible, no liability in respect of its use is acc by the editors or the manufacturers.

**Electronics Digest, Autumn 1983**

### INTRODUCTION/MICROPROCESSORS

# INTRODUCTION

This is the second of two editions of **Electronics Digest** Data specials – the first, featuring discrete components, linear ICs, CMOS and TTL, appeared in the Spring '82 edition of ED. This volume is dedicated to microprocessors and their support ICs.

The aim in this Data Digest is to provide enough information to enable constructors to sort out which chips they want to use for a particular application. With this in mind we have chosen a selection of CPUs and support chips, mostly (but not exclusively) eight-bit, which are frequently used by amateur constructors and are obtainable from most electronics suppliers. These ICs are simple enough for most amateur designers for most common uses, but not so simple as to be very restricting.

Condensed data is given on a selection of ICs considered to be useful to the amateur constructor and the small industrial user, perhaps foraying into the field of microprocessors seriously for the first time.

The ICs chosen are firstly those most commonly used – the 6800 and 8080 have topped the tables for a time, but data on these has been omitted because there are now more suitable basic ICs in the family for new designs.

Brief information on the much more advanced devices has been included for interest, and to give a perspective on the field, even though it is unlikely that the amateur or newcomer will want to use these ICs at first.

In order to give a reasonable amount of information on the basic processors chosen, only standard variants are specifically referred to. However, most microprocessors are available in different speed variants, and often there are CMOS versions available for low power consumption applications. A good example is the Hitachi HD6300 series, which are CMOS versions of the 6800 series. CMOS processors, being more specialised, cost more than the standard versions.

The data given for each chip is by no means the complete manufacturer's data! In order to get a reasonable selection into the available space, firstly, information which would only be required when carrying out the detailed design of a system has been omitted. Secondly, points that are unusual have been given preference over more pedestrian information which is common to many chips. One example: every microprocessor can add and subtract, but few can multiply. Such special features could be the deciding factor between one chip and another: for example, the presence of a counter-timer and the ability to do reciprocals, to provide rapid, accurate readout of low frequencies.

So the selection of data is not identical for each IC covered. We have used, generally, the points which we think are of greatest interest.

Finally, more information has been provided on ICs in fairly common use, so that a humble PIA may have as much space devoted to it as a complex all-singing, all-dancing disk controller. In any event, once a choice has been made the manufacturer's data sheet will be needed to complete the design.

# MICROPROCESSORS

Almost everyone has heard about the so-called 'chip'. The original 'chip' – the integrated circuit – has been around since long before microprocessors appeared, and in many ways the latter can be considered the logical extension of the former.

The microprocessor is different from other ICs, because its high level of integration and programmability open the door to electronic control systems and computers which are economical, yet sophisticated enough to find widespread application.

Among other things, this has led to fears that jobs will be lost to microprocessor-based control systems where previously automatic control equipment would have been prohibitively expensive.

So both in technical terms and in terms of general public interest, microprocessors are significantly different from other ICs.

Firstly, a microprocessor can carry out sequential instructions under program control. One type of processor, with memory and support ICs, can perform an enormous range of tasks. This can safely be mass produced in large enough quantities to make it much cheaper than any moderately complex collection of logic gates. Typically, the microprocessor can carry out logical (AND, OR, etc.) operations, arithmetic instructions (ADD, SUBTRACT, etc.). various shifts and moves, and, of great importance, Conditional Jumps.

A Conditional Jump is an instruction which will transfer an execution to another part of the program if a certain condition is/is not met. Simple examples are 'branch if zero', 'branch if not zero', 'branch if plus', 'branch if minus', 'branch if equal', or 'branch if not equal'.

This type of instruction is essential – without this, it could perform only limited sets of predetermined functions, and would be equivalent only to a set of combinational logic, or perhaps a set of cam operated switches driven by a clock motor!

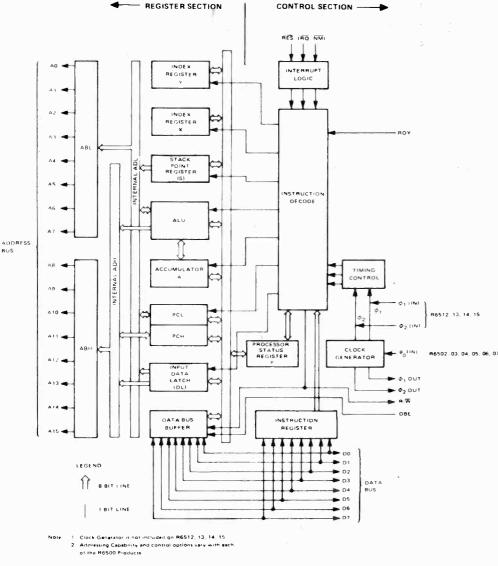

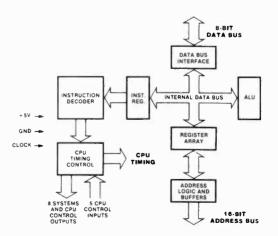

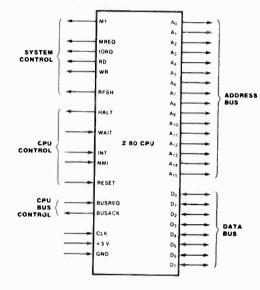

To carry out its functions, the microprocessor has internal

MICROPROCESSORS

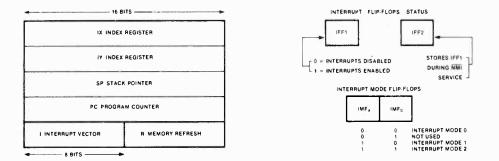

registers. These are used to store data while it is being worked on. Two essential registers are the Accumulator, and the Program Counter.

The Accumulator is used in virtually all logic and arithmetic operations. Some processors have more than one register able to be used as the accumulator, and certain eight bit processors can do some sixteen bit operations.

The program counter stores the address of the next instruction to be executed. It is automatically incremented on fetching the previous instruction. In an eight bit processor, the PC is normally sixteen bits wide.

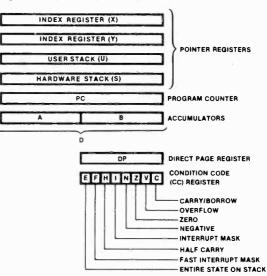

Other registers of which most simple processors have a selection are: Stack Pointer (SP), Index Registers (IX), an extra Accumulator (ACCB) and a Condition Code Register (CC).

In writing a program of any complexity, there are sequences of instructions, eg. to multiply two eight bit numbers, that are used several times. It's often more convenient (and comprehensible) to use subroutines which will carry out these sequences of instructions each time they are called.

The subroutine resides at an address clear of the main program, and in order to return to the same place in the main program, the PC and any other registers affected by the subroutine are stored in specific order on a Stack.

A Stack is an area of memory reserved by the programmer for such use, and as each register is added, the SP is counted onwards by one, to point to the address of the last register stored.

Once the subroutine is finished, the return to the main program is carried out by loading registers back from the stack in reverse order. It is possible to have one subroutine call another in, and have an orderly return through the various levels. The stack can grow quite large in this way.

Anyone who has written programs in BASIC will be familiar with the concept of arrays: they are tables of data to be processed. To provide a similar function on a microprocessor the IX may be used. The number in this may be output onto the address bus, and may be incremented or decremented to address data in sequential order.

The Condition Code register has its individual bits set to indicate conditions such as overflow, carry etc. It may also have bits set to indicate results of comparisons.

The Bus is a group of eight, sixteen or however many lines to carry data, addresses, etc., often in either direction. Some processors have multiplexed buses in which, for example, eight of the sixteen address lines are multiplexed with the data, and one signal is provided to indicate when the lines are used for address or data.

Another important function of microprocessors is Interrupts. If a microprocessor-based system must respond to the operator pushing a switch, but must (of course) be carrying out other tasks meanwhile, the switch may be connected to an interrupt pin.

When the pin gets a signal, a subroutine called Interrupt Service Routine will be called to take appropriate action.

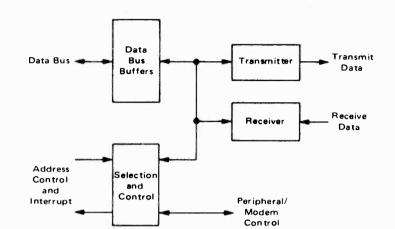

A microprocessor must have support ICs of various types. The most essential is the program memory, normally stored on a Programmable Read Only Memory (PROM). It may also need input/output (I/O) chips, for example to light up a display, or accept input from a keyboard.

Commonly used PROMs are erasable by UV light. Sunlight will not quickly erase them, as the dominant wavelengths are not short enough, but an opaque adhesive label over the window preserves data for a longer period. Typical storage times of ten years are quoted.

The information is stored as an electronic charge on an isolated piece of metalization on the chip, arranged so that

the charge may bias On or Off a FET. The charge is placed on the gate by application of a high voltage pulse which causes electrons to tunnel through the insulating layer which they could not normally cross. UV excites the bound electrons in the insulation so that the charge can slowly leak away, as though through a very high-value resistor.

There are many processors available – from four to 32 bits – there is even a one-bit controller IC, the MC14500 which could be considered a microprocessor!

The main ones included here are members of the 8080 family and the 6800 family. Some sample comparisons can be made:

• The 8080 has a good selection of internal registers which can often be used in pairs for double byte operations.

• The support ICs for the 8080/8085 group are "mix-andmatch" – for example, one type, the 8155/8156, has 22 I/O lines (eight plus eight plus six), a timer and 256 bytes of RAM included within it.

• By contrast, the 6802 is stronger on indexed addressing and operations directly on memory, where the 8085 is weak. Its 256 bytes of built-in RAM has a battery backup mode to retain the information while the power is off – the current consumption in this mode is, of course, very low.

● The 6802 does not have the 8085's good selection of internal registers, nor are its support chips so much the "mixed flavours" types. However, the nearest equivalent to the 8155, the 6821, is an I/O port which can have its individual pins programmed as input or output, while the 8155 can only be programmed in three blocks.

• The 6502 has much hardware compatibility with the 6802, but its instruction set is different and includes some BCD operations, making it more suitable for home computers.

• The TMS9995 is a sixteen bit processor, but is organised to eight bit memories. It has many advanced features, such as an on-chip timer, RAM, etc. It could be compared with the more advanced chips from the other ranges, such as the 8088, 6809.

Though for most microprocessor families there is a primary manufacturer, the originator of the family, often a number of other manufacturers produce equivalent chips, which may be a minor variation or enhancement of the original. In order to give an idea of what is available, a selection of different manufacturers' data has been used for the different processors within each family.

Now read on ....

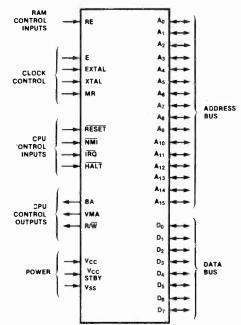

## FAIRCHILD F6800 SERIES General Information

The 6800 was originally developed by Motorola at about the same time that Intel introduced the 8080. Unlike other processors of its day, the 6800 had a single supply rail. Its level of popularity was

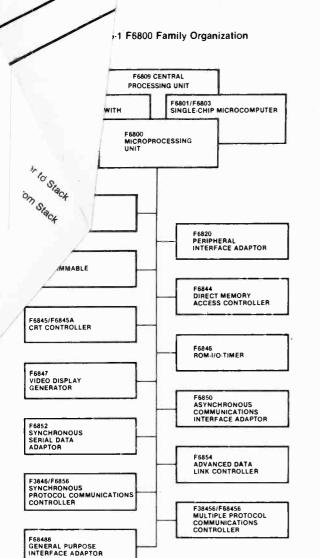

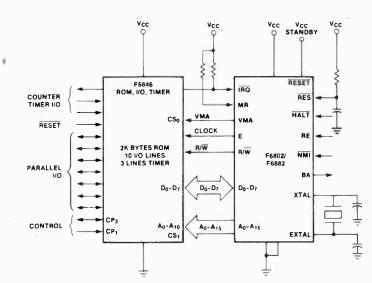

The Fairchild F6800 microprocessor family is a set of 8-bit MOS devices that offers a complete and constantly growing selection of microprocessors having a powerful instruction set. As shown in figure 5-1, the F6800 family now includes seven different CPUs (described in table 5-1), supported by such circuits as synchronous and asynchronous controllers for data communications, timers, a direct memory access controller, CRT controllers, RAMs, ROMs, and EPROMs (described in table 5-2). similar to that of the 8080. Developments of the 6800 are currently popular and useful, and the family is now covered by many manufacturers.

#### Table 5-1 F6800 Microprocessor Family CPUs

| Device No. | No. of<br>Pins | Power<br>Supply | External<br>Addressing | Data<br>Length<br>(Bits) | Clock | No. of<br>Basic<br>Instructions | Bytes<br>(RAM) | Bytes<br>(ROM) | No. of<br>I/O<br>Lines | Other<br>I/O | Timer  |

|------------|----------------|-----------------|------------------------|--------------------------|-------|---------------------------------|----------------|----------------|------------------------|--------------|--------|

| F6800      | 40             | +5 V            | 64K                    | 8                        | No    | _                               | _              | _              | _                      |              |        |

| F6801      | 40             | +5 V            | 64K                    | 8                        | Yes   | 82                              | 128            | 2K             | 31                     | Serial       | 16-Bit |

| F6802      | 40             | +5 V            | 64K                    | 8                        | Yes   | 72                              | 128            | _              | _                      | _            | _      |

| F6803      | 40             | +5 V            | 64K                    | 8                        | Yes   | 82                              | 128            | _              | 13                     | Serial       | 16-Bit |

| F6808      | 40             | + 5 V           | 64K                    | 8                        | Yes   | 72                              | _              |                | -                      |              |        |

| F6809      | 40             | +.5 V           | 64K                    | 8                        | Yes   | 59                              |                | _              | _                      | _            | _      |

| F6882      | 40             | + 5 V           | 64K                    | 8                        | Yes   | 72                              | 128            | _              | _                      | _            | _      |

#### Table 5-2 F6800 Peripheral Devices

| Туре                | Number  | Name                                             | Comment                                 |

|---------------------|---------|--------------------------------------------------|-----------------------------------------|

| General-Purpose     | F6820   | Peripheral Interface<br>Adapter                  | Twenty I/O Lines                        |

| General-Purpose     | F6821   | Peripheral Interface<br>Adapter                  | Twenty I/O Lines                        |

| General-Purpose     | F6840   | Programmable Timer Module                        | Three-to 16-Bit Timers                  |

| General-Purpose     | F68488  | General-Purpose<br>Interface Adapter             | IEEE-488 Bus Controller                 |

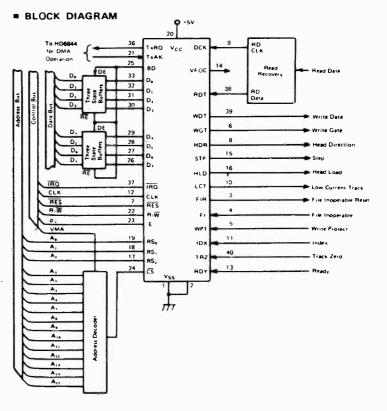

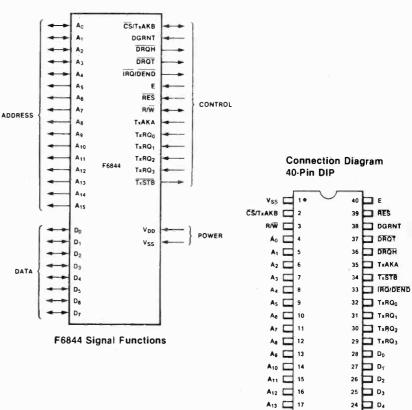

| Special Function    | F6844   | Direct Memory Access<br>Controller               | Three I/O Channels                      |

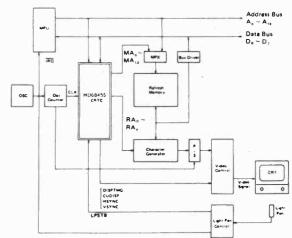

| Special Function    | F6845   | CRT Controller                                   | Available in Interlace or Non-Interlace |

| Special Function    | F6846   | ROM, I/O, Timer                                  | 2K × 8 ROM, Parallel I/O, Timer         |

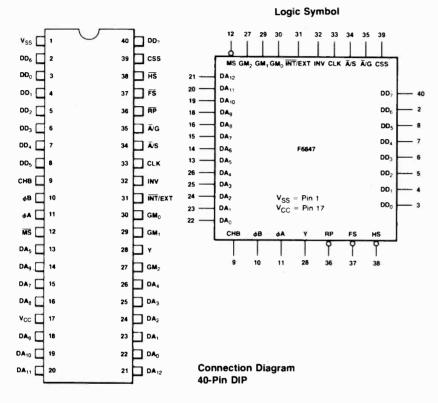

| Special Function    | F6847   | Video Display Generator                          | Low-Cost Video Controller               |

| Data Communications | F6850   | Asynchronous Communications<br>Interface Adapter | 1<br>                                   |

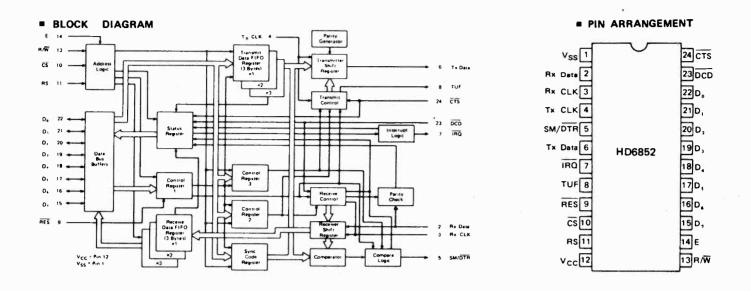

| Data Communications | F6852   | Synchronous Serial Data<br>Adapter               |                                         |

| Data Communications | F6854   | Advanced Data Link<br>Controller                 | HDLC/SDLC                               |

| Data Communications | F6856/  | Synchronous Communications                       | HDLC/SDLC/BTSYNC                        |

|                     | F3846   | Protocol Controller                              |                                         |

| Data Communications | F68456/ | Multi-Protocol                                   | HDLC/SDLC/BISYNC/ASYNC                  |

|                     | F38456  | Communications Controller                        |                                         |

| Memory              | F6810   | 128 × 8-Bit Static RAM                           |                                         |

Data courtesy of Fairchild Semiconductors Ltd.

This is our interpretation of Fairchild data on devices in their F6800 family and is believed to be accurate and reliable. However, neither Fairchild nor ourselves can assume responsibility for its use or for use of any circuitry described. For more current, detailed information, please contact one of their franchised distributors, not Fairchild themselves.

#### Instruction Set

Because a single instruction set is inadequate for the number and flexibility of devices in the F6800 family, it has been necessary to develop three such sets, each serving a portion of the family.

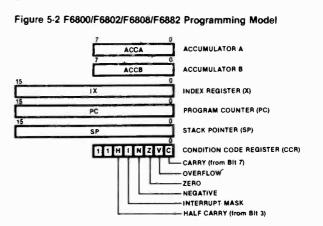

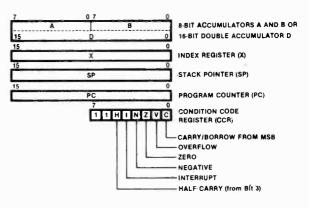

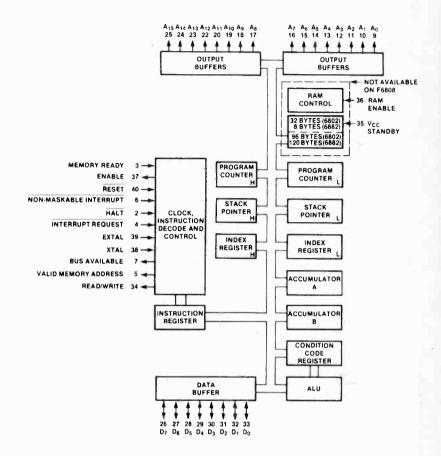

The basic instruction set, comprising 72 instructions, is supported by the F6800, F6802, F6808, and F6882; figure 5-2 is the associated programming model. An expanded instruction set, consisting of the basic set plus several additional instructions, is supported by the F6801 and F6803; figure 5-3 illustrates the associated programming model. The expanded instruction set is upward-compatible with the basic set (that is, programs written using either are interchangeable, provided that the additional instruction's are not involved). Both the basic and expanded instruction sets are described in table 5-3.

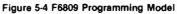

The instruction set supported by the high-performance F6809 is similar in structure to the basic and expanded sets, but is not upward-compatible. It is greatly enhanced to take fullest advantage of the powerful F6809 architecture. Figure 5-4 illustrates the F6809 programming model and table 5-4 describes the instruction set.

F6800 Family

Figure 5-3 F6801/F6803 Programming Model

#### Table 5-3 Basic and Expanded Instruction Sets

| Instruction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            | Instruction         | Description                        |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------|------------------------------------|

| ABA         | Add Accumulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |                     |                                    |

| ABX         | Add Accumulator B to Index Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            | NEG                 | Negate                             |

| ADC         | Add With Carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            | NOP                 | No Operation                       |

| ADD and     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |                     |                                    |

| *ADDD       | Add Double Accumulator to Memory; Leave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Sum In Dauble 4            | ORA                 | Inclusive OR Ac                    |

| AND         | Logical AND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Sum in Double Accumulation |                     |                                    |

| ASL         | Arithmetic Shift Left                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            | PSH                 | Push Data                          |

| *ASLD       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            | *PSHX               | Push Index Regist                  |

| ASR         | Double Accumulator Shift Left; Clear LSB; S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Shift MSB into C-Bit       | PUL                 | Pull Data                          |

|             | Arithmetic Shift Right                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            | * PULX              | Pull Index Register t              |

| BCC         | Branch if Carry Clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            | RJOL                | Rotate Left                        |

| BCS         | Branch if Carry Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            | ROR                 | Rotate Right                       |

| BEO         | Branch if Equal To Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            | RTI                 | Return from Interrupt              |

| BFE         | Branch if Greater Than or Equal To Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            | RTS                 | Return from Subroutine             |

| BGT         | Branch if Greater Than                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |                     | Hetan nom Sabroutine               |

| BHI         | Branch if Higher Than                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            | SBA                 | Subtract Accumulators              |

| *BHS        | Branch if Higher Than or Same As                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            | SBC                 | Subtract With Carry                |

| BIT         | Bit Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            | SEC                 | Set Carry                          |

| BLE         | Branch if Less Than or Equal To                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            | SEL                 | Set Interrupt Mask                 |

| BLO         | Branch if Lower Than                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            | SEV                 | Set Overflow                       |

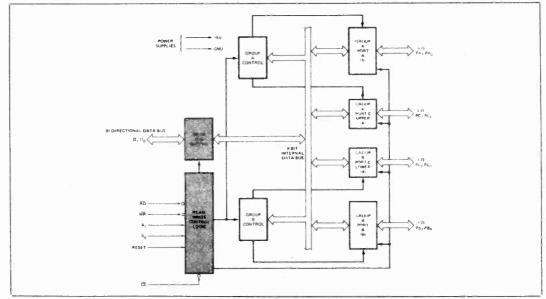

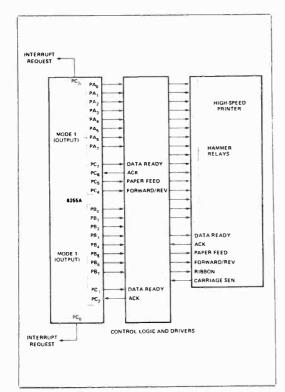

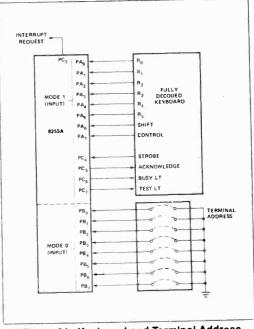

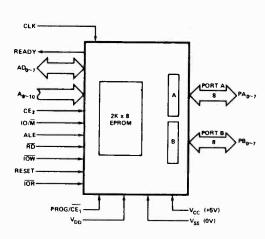

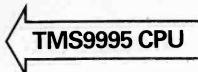

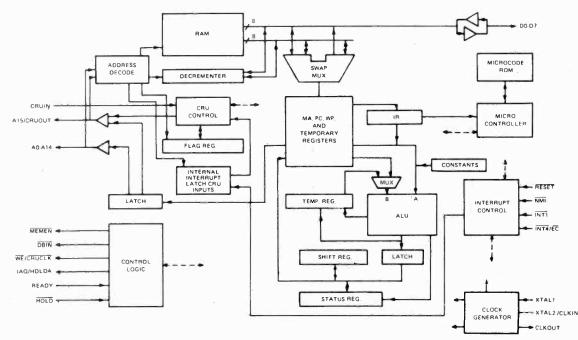

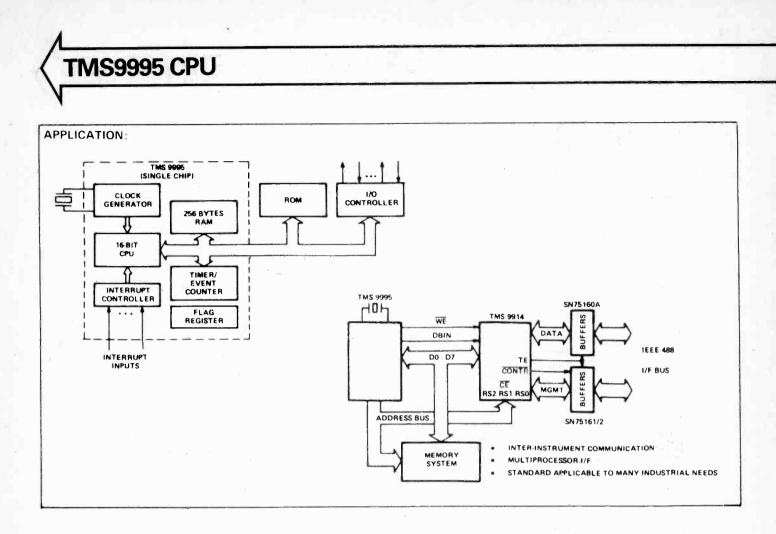

| BLS         | Branch if Lower Than or Same As                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            | STA                 | Store Accumulator                  |